![]() Bên trong kiến trúc Core của Intel (Phần 1)

Bên trong kiến trúc Core của Intel (Phần 1)

Khối thực thi

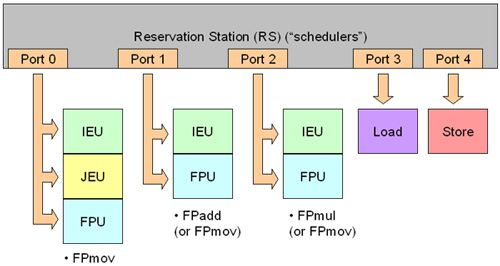

Pentium M có 5 cổng gửi đi được đặt trên trạm dành riêng Reservation Station của nó, nhưng chỉ có hai cổng được sử dụng để gửi đi các chỉ lệnh micro-ops đến các khối thực thi. Ba chỉ lệnh còn lại được sử dụng bởi các khối có liên quan đến bộ nhớ (Load, Store Address và Store Data). Kiến trúc Core cũng có 5 cổng gửi đi như vậy nhưng ba trong số chúng được sử dụng cho việc gửi các chỉ lệnh nối micro-ops đến các khối thực thi. Điều đó có nghĩa rằng các CPU đang sử dụng kiến trúc Core đó có thể gửi ba chỉ lệnh micro-ops đến khối thực thi trên một chu kỳ clock.

Kiến trúc Core cung cấp một FPU mở rộng và một IEU mở rộng (ALU) khi chúng ta mang ra so với kiến trúc Pentium M. Điều này có nghĩa rằng kiến trúc Core có thể xử lý đến ba chỉ lệnh số nguyên trên một chu kỳ clock, trong khi Pentium M chỉ có hai.

Tuy nhiên không phải tất cả các chỉ lệnh toán học đều có thể được thực thi trên tất cả các FPU. Như những gì bạn có thể quan sát được trong hình 2, các toán tử nhân floating-point chỉ có thể được thực thi trong FPU thứ ba và phần thêm vào floating-point chỉ có thể được thực thi trên FPU thứ hai. Các chỉ lệnh Fpmov có thể được thực thi trên FPU thứ nhất hoặc trên hai FPU khác nếu không có chỉ lệnh phức tạp hơn (FPadd or FPmul) đã sẵn sàng được gửi đến chúng. Các chỉ lệnh MMX/SSE đều được xử lý bởi FPU.

Trong hình 2 bạn sẽ thấy sơ đồ khối chính của các khối thực thi trong kiến trúc Core.

Hình 2: Các khối thực thi trong kiến trúc Core

Một sự khác nhau lớn giữa hai kiến trúc Pentium M và Pentium 4 với kiến trúc Core là trên kiến trúc Core, các khối Load và Store có khối tạo địa chỉ của riêng nó nhúng trong. Pentium 4 và Pentium M có các khối tạo địa chỉ riêng và trên Pentium 4 ALU đầu tiên được sử dụng để lưu dữ liệu trên bộ nhớ.

Dưới đây là những giải thích nhỏ về những khối có trong CPU này:

- IEU: Instruction Execution Unit là nơi các chỉ lệnh được thực thi. Khối này cũng được biết đến là khối ALU (Arithmetic and Logic Unit). Các chỉ lệnh thông thường cũng được biết là các chỉ lệnh số nguyên.

- JEU: Jump Execution Unit xử lý rẽ nhánh và cũng được biết đến với tên Branch Unit.

- FPU: Floating-Point Unit. Khối này chịu trách nhiệm cho việc thực thi các biểu thức toán học floating-point và cũng cả các chỉ lệnh MMX và SSE. Trong CPU này, các FPU không “hoàn thiện” vì một số kiểu chỉ lệnh (FPmov, FPadd và FPmul) chỉ được thực thi trên các FPU nào đó:

- FPadd: Chỉ có FPU này mới có thể xử lý các chỉ lệnh cộng floating-point như ADDPS.

- FPmul: Chỉ có FPU này mới có thể xử lý các chỉ lệnh nhân floating-point như MULPS

- FPmov: Các chỉ lệnh cho việc nạp hoặc copy một thanh ghi FPU, như MOVAPS (được dùng để truyền tải dữ liệu đến thanh ghi SSE 128-bit XMM). Kiểu chỉ lệnh này có thể được thực thi trên các FPU, nhưng chỉ trên các FPU thứ hai và thứ ba nếu các chỉ lệnh Fpadd hay Fpmul không có trong Reservation Station.

- Load: khối này dùng để xử lý các chỉ lệnh yêu cầu dữ liệu được đọc từ bộ nhớ RAM.

- Store Data: Khối này xử lý các chỉ lệnh yêu cầu dữ liệu được ghi vào bộ nhớ RAM.

Lưu ý rằng các chỉ lệnh phức tạp có thể mất đến một số chu kỳ clock trong khi xử lý. Chúng ta hãy lấy một ví dụ về cổng 2, nơi khối FPmul nằm ở đó. Khi khối này đang xử lý một chỉ lệnh rất phức tạp phải mất đến vài chu kỳ clock để được thực thi thì cổng 2 sẽ không chết: nó sẽ luôn gửi các chỉ lệnh đơn giản đến IEU trong khi FPU đang bận.

Đường dẫn 128-bit bên trong

Một tính năng khác có trong kiến trúc Core là đường dẫn dữ liệu 128 bit bên trong. Trong các CPU trước, đường dẫn dữ liệu bên trong chỉ có 64bit. Đây là một vấn đề đối với các chỉ lệnh SSE, chỉ lệnh được gọi là XMM có dài 128 bit. Chính vì vậy khi thực thi một chỉ lệnh đã biến đổi thành 128 bit dữ liệu thì toán tử này được chia thành hai toán tử 64bit.

Đường dữ liệu 128 bit mới làm cho kiến trúc Core trở nên nhanh hơn trong việc xử lý các chỉ lệnh SSE có 128 bit dữ liệu.

Kiến trúc nhớ mới

Kiến trúc nhớ mới là kỹ thuật tăng tốc thực thi các chỉ lệnh có liên quan đến bộ nhớ.

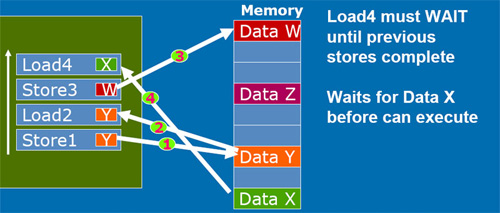

Tất cả các CPU của Intel từ Pentium Pro đều có cơ chế không tuân theo trình tự (out-of-order), cơ chế này cho phép CPU có thể thực thi các chỉ lệnh không phụ thuộc theo bất cứ một thứ tự nào. Những gì xảy ra với các chỉ lệnh liên quan đến bộ nhớ được thực thi theo kiểu truyền thống diễn ra theo một thứ tự giống hệt với thứ tự chúng xuất hiện trong chương trình. Ví dụ, nếu chương trình gốc có một chỉ lệnh như “store 10 at address 5555” và sau đó là một chỉ lệnh “load data stored at 5555”, thì chúng sẽ không thể được đảo ngược (nghĩa là được thực thi không tuân theo thứ tự) hoặc chỉ lệnh thứ hai sẽ lấy sai dữ liệu, vì dữ liệu ở địa chỉ 5555 đã bị thay đổi bởi chỉ lệnh thứ nhất.

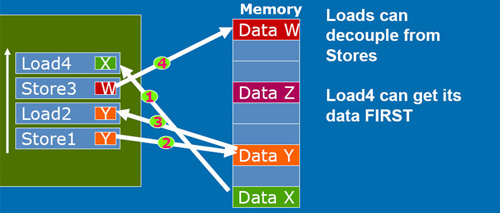

Những gì mà cơ chế kiến trúc nhớ mới thực hiện là định vị và thực thi các chỉ lệnh có liên quan đến bộ nhớ để có thể thực thi không theo thứ tự, tăng tốc độ thực thi của chương trình (chúng tôi sẽ giải thích thêm về điều này được thực hiện như thế nào).

Trong hình 3, bạn có một ví dụ về một CPU không có cơ chế nhớ này (nghĩa là tất cả các CPU không được xây dựng trên kiến trúc Core). Như những gì bạn có thể nhìn thấy, CPU phải thực thi các chỉ lệnh khi chúng xuất hiện trong chương trình gốc. Ví dụ, chỉ lệnh “Load4” không liên quan tới bất kỳ đến bộ nhớ nào và có thể được thực thi trước, mặc dù vậy nó vẫn phải đợi tất cả các chỉ lệnh khác.

Hình 3: CPU không có kiến trúc nhớ mới

Trong hình 4, bạn sẽ thấy cách chương trình trong hình 3 làm việc như thế nào trên CPU có kiến trúc Core. Nó “biết” rằng chỉ lệnh “Load4” không có liên quan đến các chỉ lệnh khác và có thể được thực thi trước.

Hình 4: CPU với cơ chế nhớ mới.

Điều này đã cải thiện được hiệu suất của CPU vì lúc này chỉ lệnh “Load4” sẽ được thực thi ngay từ đầu, CPU có dữ liệu cần thiết cho việc thực thi các chỉ lệnh khác cần đến giá trị “X” để được thực thi.

Trong các CPU thông thường, nếu sau khi chỉ lệnh “Load4” này có chỉ lệnh “Add 50”, thì chỉ lệnh “Add 50” (và tất cả các chỉ lệnh khác phụ thuộc vào kết quả đó) sẽ phải đợi các chỉ lệnh khác như đã thể hiện trong hình 3 để được thực thi. Với kiến trúc nhớ mới này, các chỉ lệnh đó có thể được thực thi sớm, vì CPU lúc này sẽ có được giá trị “X” từ sớm.

Điều chỉnh tiết lưu công suất

Với việc điều chỉnh tiết lưu công suất tiên tiến, kiến trúc Core làm tiết kiệm được nhiều năng lượng tiêu thụ hơn so với các CPU trước đó. Tính năng này cho phép CPU có thể tắt các khối đang không được sử dụng ở thời điểm đó. Ý tưởng này thậm chí còn cho phép nhiều ưu việt hơn vì khi CPU có thể tắt các phần cụ thể bên trong mỗi khối CPU để tiết kiệm năng lượng, tốn ít công suất và cải thiện được thời gian sử dụng của pin (trong trường hợp xét đến các CPU di động).

Một khả năng tiết kiệm năng lượng khác của kiến trúc Core là chỉ bật các bit cần thiết trong các bus bên trong CPU. Nhiều bus bên trong của CPU được kích thước một cách cồng kềnh và lãng phí. Chính vì vậy thay cho việc bật tất cả ví dụ 480 làn dữ liệu của một bus nào đó thì CPU có thể chỉ cần bật 32 làn dữ liệu của nó, tất cả các dữ liệu trong làn đó đều cần thiết cho việc truyền tải chỉ lệnh 32bit.

* Có thể hơi khó hiểu ở tuyên bố này, vì bạn vẫn thường nghe thấy rằng kiến trúc của Intel sử dụng các chỉ lệnh 32bit, vì vậy chúng tôi cần đưa ra giải thích này để làm sáng tỏ vấn đề.

Bên trong CPU, những gì được xem xét ở một chỉ lệnh là mã thao tác (opcode) của chỉ lệnh đó (ngôn ngữ máy tương đương với ngôn ngữ chỉ lệnh assembly) cộng với tất cả các dữ liệu được yêu cầu. Điều này là vì để được thực thi, chỉ lệnh phải nhập vào cơ chế thực thi “hoàn tất”, nghĩa là cùng với tất cả các dữ liệu được yêu cầu. Cũng theo cách đó, kích thước của mỗi mã thao tác chỉ lệnh x86 là một biến và không cố đinh là 32bit như những gì bạn vẫn nghĩ. Ví dụ, một chỉ lệnh “mov eax, (32-bit data)”, dùng để lưu (32-bit data) và thanh ghi EAX của CPU được xem xét bên trong như một chỉ lệnh 40bit (mov eax dịch vào 8-bit opcode cộng với 32bit dữ liệu). Việc các chỉ lệnh có số chiều dài khác nhau là những gì đặt trưng cho tập chỉ lệnh CISC (Complex Instruction Set Computing).

AI

AI  Hướng dẫn AI

Hướng dẫn AI  ChatGPT

ChatGPT  Gemini

Gemini  Thư viện Prompt

Thư viện Prompt  Công nghệ

Công nghệ  Học IT

Học IT  Tiện ích

Tiện ích

Làng Công nghệ

Làng Công nghệ  Chuyện công nghệ

Chuyện công nghệ

AI

AI  Hướng dẫn AI

Hướng dẫn AI  Công nghệ

Công nghệ  Ứng dụng

Ứng dụng  Hệ thống

Hệ thống  Game - Trò chơi

Game - Trò chơi  iPhone

iPhone  Android

Android  Học CNTT

Học CNTT  Hàm Excel

Hàm Excel  Download

Download  Khoa học

Khoa học  Cuộc sống

Cuộc sống