Nếu bạn không chắc chắn về thuật ngữ “FlipChip”, hướng dẫn này sẽ giúp bạn hiểu rõ hơn về công nghệ FlipChip packaging (hay còn gọi là đóng gói chip kiểu lật).

Công nghệ FlipChip package đã tồn tại được 3-4 thập kỷ, với vai trò ban đầu là một giải pháp cho số lượng pin (chân) lớn và yêu cầu gói hiệu suất cao. Lúc đầu, phần lớn các ứng dụng FlipChip package là SoC có số pin lớn (bao gồm hơn 700 pin), mà loại gói Wire-Bond BGA điển hình không thể xử lý đúng cách. Ngoài ra, một số SoC kết hợp các interface tốc độ cao (bao gồm RF) mà các wirebond (nối dây - quá trình kết nối dây dẫn trên đế chip với những sợi cực mảnh từ các mạch điện trên chip) có thể không hỗ trợ do cảm kháng của dây cao.

Nhu cầu về FlipChip package đã tăng lên trong thập kỷ qua và được thúc đẩy bởi thị trường di động, nơi kích thước gói và hiệu suất tín hiệu đóng vai trò rất quan trọng.

Ngày nay, công nghệ FlipChip package cung cấp một loạt các lợi ích bao gồm: Số pin lớn, mật độ tín hiệu cao, công suất phát tán tốt hơn, cảm kháng tín hiệu thấp và kết nối nguồn/đất tốt. Các FlipChip package khá phổ biến hiện nay và bạn có thể tìm thấy chúng trong các thiết bị nhỏ gọn như những mẫu điện thoại di động cao cấp.

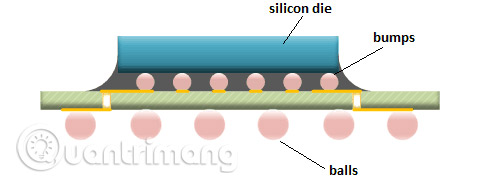

Về cơ bản, cái tên FlipChip mô tả phương pháp được sử dụng để kết nối một khuôn bán dẫn với đế chip. Trong một FlipChip package, các khuôn bị va đập và sau đó, lật lên đế chip, do đó nó có tên là FlipChip.

Nhờ thực tế là các bump (bi vàng) được phân phối trên toàn bộ chip, chứ không chỉ nằm trên cạnh khuôn, do đó các pad (miếng đệm) có thể được đặt trên khắp bề mặt khuôn. Điều này cho phép các nhà thiết kế đặt nhiều pad hơn cho mỗi khuôn, giảm kích thước chip và tối ưu hóa tính toàn vẹn tín hiệu.

Đế chip cung cấp khả năng kết nối với PCB bên ngoài thông qua các solder ball (bi chì). Kích thước đế chip, số lượng lớp và tính chất vật liệu có tác động trực tiếp đến tổng chi phí. Trong một số trường hợp, đế chip có thể là yếu tố đắt tiền nhất trong FlipChip package.

Các bump được đặt trực tiếp trên những I/O pad và do đó, chúng kết nối khuôn với đế. Sau quá trình bumping (bumping là một công nghệ xử lý cấp độ wafer tiên tiến, trong đó, các solder ball/bump được hình thành trên các tấm wafer), wafer được chia nhỏ và cuối cùng, các khuôn sẽ lật lên phần đế chip. Các bump kết nối khuôn và đế chip với nhau thành một package duy nhất.

Công nghệ đế chip

Đế chip FlipChip là một PCB nhỏ nằm bên trong package và rất giống với bất kỳ PCB nào khác. Sự khác biệt là kích thước đế chip nhỏ hơn nhiều so với hầu hết các PCB bạn đã thấy.

Thiết kế đế chip bao gồm layout của tất cả tín hiệu từ những bi bên ngoài package đến các bump pad.

Đế chip có thể được chế tạo bằng nhiều vật liệu khác nhau: Gỗ Laminate, sứ, v.v... Quy tắc thiết kế layout đế chip của các nhà cung cấp không giống nhau.

Đế chip có thể bao gồm nhiều lớp khác nhau, từ 2-18 lớp để cho phép định tuyến tất cả các tín hiệu.

Công nghệ Wafer Bumping

Các wafer bump cung cấp kết nối giữa khuôn và đế chip, thông qua độ cảm kháng và điện trở thấp, cũng như vật liệu sản xuất chất lượng cao, đáng tin cậy.

Wafer bump có thể được cấu tạo từ vật liệu eutectic, chì thiếc, không chì, chì cao hoặc công nghệ Cu pillar. Kích thước và khoảng cách bump của mỗi nhà lắp ráp không giống nhau.

Quy trình lắp ráp FlipChip

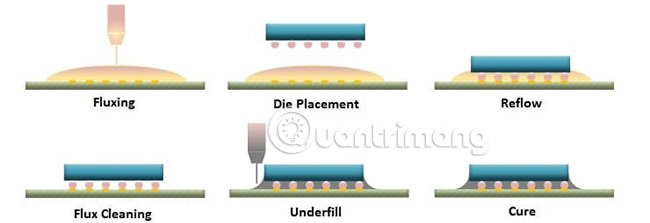

Trong bước xử lý cuối cùng của quy trình wafer bumping, các bump được đặt trên các pad của chip có thể được tìm thấy ở mặt trên của wafer. Để chip được kết nối hoặc gắn vào đế, khuôn được lật và đặt thẳng hàng với các pad nằm trên đế.

Có 6 bước trong quá trình tạo FlipChip, cung cấp cho nó tính linh hoạt đáng kể khi kết nối các thiết bị.

Ưu và nhược điểm của FlipChip

Các package FlipChip có những ưu điểm và nhược điểm, bắt nguồn từ phương pháp lắp ráp tạo ra một con chip nhỏ gọn hơn rất nhiều so với các giải pháp wirebond trước đây. Bởi vì chip được kết nối trực tiếp với bảng mạch, nên dây dẫn ngắn hơn, tạo ra độ cảm kháng ít hơn. Điều này có nghĩa là các thiết bị hiện có thể truyền tín hiệu ở tốc độ cao hơn đáng kể, đồng thời tản nhiệt hiệu quả hơn.

AI

AI  Hướng dẫn AI

Hướng dẫn AI  ChatGPT

ChatGPT  Gemini

Gemini  Thư viện Prompt

Thư viện Prompt  Công nghệ

Công nghệ  Học IT

Học IT  Tiện ích

Tiện ích

AI

AI  Hướng dẫn AI

Hướng dẫn AI  Công nghệ

Công nghệ  Ứng dụng

Ứng dụng  Hệ thống

Hệ thống  Game - Trò chơi

Game - Trò chơi  iPhone

iPhone  Android

Android  Làng Công nghệ

Làng Công nghệ  Học CNTT

Học CNTT  Hàm Excel

Hàm Excel  Download

Download  Khoa học

Khoa học  Cuộc sống

Cuộc sống