Tìm hiểu cách làm việc của bộ nhớ Cache (Phần 1)

Lịch sử về Cache nhớ trên các máy tính cá nhân (PC)

Trong phần này chúng tôi chỉ quan tâm đến các khía cạnh lịch sử trước đây của bộ nhớ Cache. Nếu bạn không quan tâm đến chủ đề này thì hoàn toàn có thể bỏ qua để đọc phần tiếp theo.

Bộ nhớ Cache được sử dụng đầu tiên trên các máy tính thời 386DX. Mặc dù bản thân CPU không có bộ nhớ Cache bên trong nhưng mạch hỗ trợ của nó - chipset – có một bộ điều khiển Cache nhớ. Vì điều đó nên Cache nhớ ở thời điểm này nằm ở bên ngoài CPU và mang tính tùy chọn, nghĩa là nhà sản xuất bo mạch chủ có thể thêm vào hoặc không. Nếu bạn có một bo mạch chủ mà không có bộ nhớ Cache thì máy tính của bạn sẽ chậm hơn rất nhiều so với các máy tính có thành phần này. Số lượng bộ nhớ Cache được cung cấp khác nhau và phụ thuộc vào model của bo mạch chủ và các giá trị điển hình cho thời điểm đó là 64 KB và 128 KB. Cũng ở thời điểm này, bộ điều khiển Cache nhớ đã sử dụng một kiến trúc được biết đến với tên “write-through”, dùng cho các hoạt động ghi – nghĩa là khi CPU muốn lưu dữ liệu trong bộ nhớ thì bộ điều khiển Cache nhớ sẽ cập nhật bộ nhớ RAM ngay lập tức.

Với các bộ vi xử lý 486DX, Intel đã bổ sung thêm một số lượng nhỏ (8KB) Cache nhớ bên trong mỗi CPU. Cache nhớ bên trong này được gọi là L1 (level 1) hay “internal”, còn các Cache nhớ bên ngoài được gọi là (level 2) hay “external”. Số lượng và sự tồn tại của Cache nhớ bên ngoài phụ thuộc vào model của bo mạch chủ. Số lượng điển hình cho thời điểm đó là 128 KB và 256 KB. Sau đó các mô hình 486 đã bổ sung thêm kiến trúc Cache “write back”, đây là kiến trúc đã được sử dụng cho đến ngày nay, các hoạt động ghi của bộ nhớ RAM không được cập nhật ngay tức khắc mà CPU lưu dữ liệu trên Cache nhớ và bộ điều khiển nhớ sẽ cập nhật bộ nhớ RAM chỉ khi không có Cache.

Sau đó với các bộ vi xử lý Pentium đầu tiên, Intel đã tạo hai Cache nhớ bên trong tách biệt nhau, một cho các chỉ lệnh và một cho dữ liệu (ở thời điểm này mỗi Cache nhớ là 8 KB). Kiến trúc này vẫn được sử dụng cho đến ngày nay và đó chính là tại sao đôi khi bạn vẫn thấy Cache nhớ L1 tồn tại được ghi 64 KB + 64 KB (ví dụ) – điều này là vì có một Cache chỉ lệnh L1 64KB và một Cache nhớ dữ liệu L2 64KB. Chúng tôi sẽ giải thích cho các bạn về sự khác nhau của hai loại Cache nhớ này. Tại thời điểm đó, Cache nhớ L2 thường được đặt trên bo mạch chủ, chính vì vậy số lượng và sự tồn tại của nó phụ thuộc vào model của bo mạch chủ. Rõ ràng việc hệ thống không có Cache nhớ là một điều không thể chấp nhận. Số lượng điển hình cho thời điểm đó là 256 KB và 512 KB.

Các bộ vi xử lý AMD K5, K6 và K6-2 cũng đã sử dụng kiến trúc này, với K6-III thì có thêm Cache nhớ thứ ba (L3, level 3).

Vấn đề với Cache nhớ nằm bên ngoài L2 là nó được truy cập với tốc độ clock thấp hơn vì thế hệ 486DX2 tốc độ clock bên trong của CPU khác hoàn toàn với tốc độ clock bên ngoài của CPU. Ví dụ Pentium-200 làm việc bên trong tại tốc độ 200MHz, nó đã truy cập vào bộ nhớ Cache L2 của nó với tốc độ 66MHz.

Sau kiến trúc P6, Intel đã chuyển sang Cache nhớ từ bo mạch chủ sang bên trong CPU – điều đó đã cho phép CPU có thể truy cập với tốc độ clock bên trong – ngoại trừ Pentium II (bộ nhớ Cache không được đặt bên trong CPU nhưng trên cùng bo mạch in – nơi CPU được hàn gắn (bo mạch in này được đặt bên trong một hộp chứa)), lại chạy bằng một nửa tốc độ clock trong của CPU. Trên Celeron-266 và Celeron-300, các model này không có Cache nhớ (chính vì vậy chúng là các CPU tồi tệ nhất trong lịch sử).

Kiến trúc được sử dụng cho đến ngày nay cũng tương tự như vậy: cả hai Cache nhớ L1 và L2 đều được đặt bên trong CPU và chạy với tốc độ clock bên trong của CPU. Chính vì vậy số lượng Cache nhớ mà bạn có trên hệ thống sẽ phụ thuộc vào model của CPU; không có cách nào để có thể tăng được số lượng Cache nhớ mà không cần thay thế CPU.

Xem xét các Cache nhớ

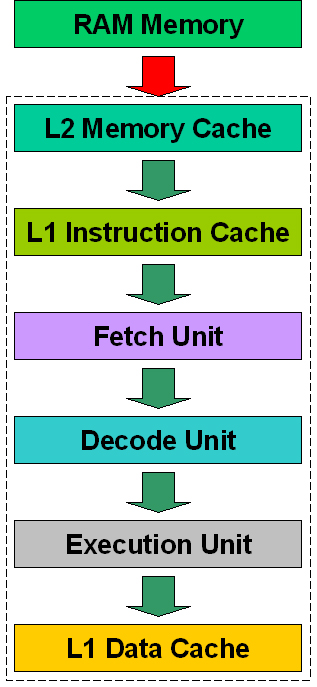

Trong hình 2, bạn sẽ thấy sơ đồ khối cơ bản của một CPU một lõi. Sơ đồ khối cụ thể sẽ thay đổi phụ thuộc vào CPU.

Hình 2: Sơ đồ khối cơ bản của một CPU

Đường chấm trên hình 2 thể hiện phần thân của CPU, vì bộ nhớ RAM được đặt bên ngoài CPU. Đường dữ liệu giữa bộ nhớ RAM và CPU có độ rộng 64 –bit thông thường (hoặc 128 khi cấu hình hai kênh được sử dụng), đang chạy với tốc độ clock nhớ hoặc clock ngoài của CPU (hoặc clock của bus nhớ, trong trường hợp đối với các bộ vi xử lý của AMD).

Tất cả các mạch bên trong phần chấm đều chạy với tốc độ clock của CPU. Phụ thuộc vào CPU mà một số thành phần bên trong nó thậm chí còn có thể chạy với tốc độ clock cao hơn. Còn đường dẫn giữa các khối CPU cũng có thể rộng hơn, nghĩa là sẽ truyền tải nhiều bit hơn trên mỗi một chu kỳ xung clock (nhiều hơn 64 hoặc 128). Ví dụ, đường dữ liệu giữa bộ nhớ Cache L2 và Cache chỉ lệnh L1 trên các bộ vi xử lý hiện đại thường có độ rộng 256-bit. Đường dữ liệu giữa Cache chỉ lệnh L1 và khối tìm nạp của CPU cũng thay đổi phụ thuộc vào mô hình của từng CPU – 128 bit là giá trị điển hình, tuy nhiên ở phần cuối của hướng dẫn này chúng tôi sẽ giới thiệu cho một bảng chỉ tiêu kỹ thuật của các Cache nhớ chính đối với các CPU được bán trên thị trường hiện nay. Số lượng truyền tải các bit trên một chu kỳ xung nhịp càng cao thì sự truyền tải càng diễn ra nhanh hơn (nói theo cách khác là tốc độ truyền tải sẽ nhanh hơn).

Nói chung, tất cả các CPU hiện đại đều có đến ba Cache nhớ: L2 là Cache nhớ lớn hơn và có thể tìm thấy ở giữa bộ nhớ RAM và Cache chỉ lệnh L1, nó nắm giữ cả các chỉ lệnh và dữ liệu; Cache chỉ lệnh L1 được sử dụng để lưu các chỉ lệnh đã được thực thi bởi CPU và lưu dữ liệu để có thể được ghi ngược trở lại bộ nhớ.

L1 và L2 có nghĩa là “Level 1” và “Level 2”, ám chỉ khoảng cách từ chúng đến lõi CPU (khối thực thi). Có một sự nghi ngờ đó là tại sao lại có đến ba Cache nhớ tách biệt (Cache nhớ dữ liệu L1, Cache nhớ chỉ lệnh L1 và Cache L2).

Để làm cho độ trễ của bộ nhớ tĩnh giảm xuống bằng “0” là một điều rất khó khăn, đặc biệt với các CPU đang chạy ở tốc độ clock rất cao. Do việc sản xuất các RAM tĩnh có độ trễ xấp xỉ “0” là rất khó nên các hãng sản xuất đã sử dụng một kiểu bộ nhớ chỉ ở trên Cache nhớ L1. Cache nhớ L2 sử dụng RAM tĩnh không nhanh bằng bộ nhớ được sử dụng trên Cache nhớ L1, điều này là do nó có độ trễ nhất định, chính vì vậy nó sẽ chậm hơn đôi chút so với Cache nhớ L1.

Hãy chú ý vào hình 2 chúng ta sẽ thấy được rằng Cache chỉ lệnh L1 làm việc giống như một “Cache đầu vào”, còn Cache dữ liệu L1 làm việc giống như một “Cache đầu ra”. Cache chỉ lệnh L1 (thường nhỏ hơn Cache L2) có hiệu quả cao hơn khi chương trình bắt đầu lặp lại một số phần nhỏ của nó, đó cũng là do các chỉ lệnh đã được yêu cầu sẽ gần khối tìm nạp hơn.

Một điều cũng hiếm khi được đề cập đến, nhưng Cache chỉ lệnh L1 cũng được sử dụng để lưu các dữ liệu khác bên cạch các chỉ lệnh đã được giải mã. Phụ thuộc vào CPU mà nó có thể được sử dụng để lưu một số dữ liệu tiền giải mã và việc rẽ nhánh thông tin (nhìn chung, dữ liệu điều khiển sẽ làm tăng được tốc độ của quá trình giải mã) và đôi khi Cache chỉ lệnh L1 còn lớn hơn cả những gì đã tuyên bố, điều này là do nhà sản xuất thường không bổ sung vào không gian mở rộng sẵn có cho những phần thông tin mở rộng này.

Trong trang các chỉ tiêu kỹ thuật của CPU, Cache L1 có thể có nhiều kiểu khác nhau. Một số nhà sản xuất liệt kê hai Cache L1 tách biệt hoàn toàn với nhau (có khi gọi Cache chỉ lệnh là “I” và Cache dữ liệu là “D”), đôi khi lại bổ sung thêm cả số lượng và phần ký hiệu “separated”, nếu “128 KB, separated” thì điều đó có nghĩa là Cache chỉ lệnh 64KB và Cache dữ liệu 64KB, một số hãng đã thực hiện để bạn có thể đoán được số lượng tổng thể và phải chia hai để có được dung lượng của mỗi Cache. Mặc dù vậy cũng có trường hợp ngoại lệ đối với các CPU được xây dựng trên kiến trúc Netburst, chẳng hạn như Pentium 4, Pentium D, Pentium 4 dựa trên Xeon và các CPU của Celeron dòng Pentium 4.

Các bộ vi xử lý dựa trên kiến trúc Netburst không có Cache chỉ lệnh L1, thay vào đó chúng có một Cache thực thi dò theo (hay có thể gọi là lần vết), Cache này được đặt giữa khối giải mã và khối thực thi, lưu các chỉ lệnh đã được giải mã. Chính vì vậy có thể nói Cache chỉ lệnh L1 là nó, nhưng được ẩn dưới một tên hoàn toàn khác và đặt ở vị trí cũng khác. Chúng ta sẽ đề cập đến vấn đề này ở đây vì đây là một lỗi rất hay mắc phải, mọi người thường nghĩ rằng các CPU Pentium 4 không có Cache chỉ lệnh L1. Điều này dẫn đến hiện tượng khi so sánh Pentium 4 với các CPU khác mọi người thường nghĩ rằng Cache L1 của nó có dung lượng nhỏ hơn, do họ chỉ tính 8KB của Cache dữ liệu L1. Cache thực thi lần vết của các CPU xây dựng trên kiến trúc Netburst là 150KB.

L2 Memory Cache trên các CPU đa lõi

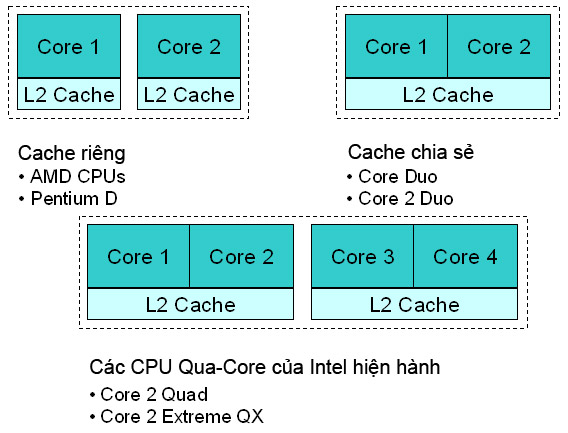

Trên các CPU có nhiều hơn một lõi, kiến trúc Cache L2 có thay đổi khá nhiều, sự thay đổi này phụ thuộc vào từng loại CPU.

Với các CPU dual-core Pentium D và AMD được xây dựng trên kiến trúc K8, mỗi lõi của CPU lại có Cache nhớ L2 riêng của chính nó. Chính vì vậy mỗi một lõi làm việc như nó đang làm việc cho một CPU độc lập.

Các CPU dual-core của Intel được xây dựng trên kiến trúc Core và Pentium M thì hai Cache nhớ L2 lại có thể được chia sẻ giữa hai lõi.

Hãng Intel nói rằng, kiến trúc chia sẻ này cho hiệu suất thực thi tốt hơn vì trên phương pháp Cache riêng vì ở một thời điểm nào đó một lõi này có thể chạy quá tải trong khi đó lõi kia lại không được sử dụng hoặc sử dụng không hết hiệu suất trên chính Cache L2 của nó. Khi xảy ra điều này, lõi chạy quá tải sẽ lấy dữ liệu từ bộ nhớ RAM chính mặc dù không gian trên Cache nhớ L2 kia hoàn toàn trống mà lẽ ra nên được sử dụng để lưu dữ liệu và tránh không để cho lõi quá tải truy cập lấy dữ liệu từ bộ nhớ RAM làm giảm hiệu suất của toàn hệ thống. Với phương pháp mới này, bộ vi xử lý Core 2 Duo với Cache nhớ L2 4MB, thì một lõi này có thể sử dụng đến 3,5MB trong khi đó lõi còn lại sử dụng 0,5MB, hoàn toàn tương phải với hệ số chia cố định 50%-50% như trên các CPU dual-core.

Có thể nói theo cách khác, các CPU quad-core hiện tại của Intel như Core 2 Extreme QX và Core 2 Quad sử dụng 2 chíp dual-core, nghĩa là việc chia sẻ này chỉ xuất hiện giữa các lõi 1 và 2, 3 và 4. Hiện nay, Intel đã lên kế hoạch cho các CPU quad-core sử dụng một chíp đơn. Với phương pháp này, Cache L2 sẽ được chia sẻ giữa bốn lõi.

Trên hình 3 bạn có thể thấy được sự so sánh giữa các giải pháp Cache nhớ L2 này.

Hình 3: So sánh các giải pháp Cache nhớ L2 hiện có trên các CPU đa lõi

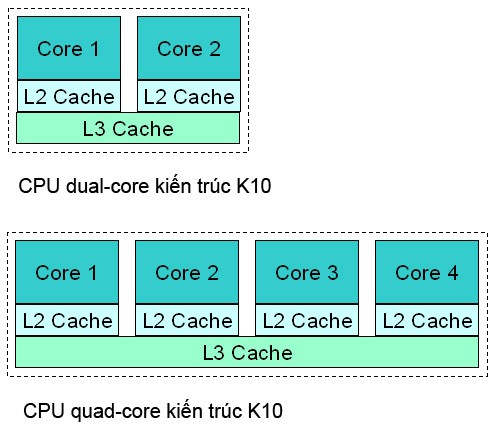

Bộ vi xử lý AMD xây dựng trên kiến trúc K10 sẽ có Cache L3 chia sẻ nằm bên trong CPU, và có một kiểu lai giữa hai phương pháp này. Vấn đề này được thể hiện trên hình 4. Kích thước của Cache này sẽ phụ thuộc vào mô hình của CPU, cũng giống như những gì xảy ra với kích thước của Cache L2.

Hình 4: Kiến trúc Cache K10

![]() Tìm hiểu cách làm việc của bộ nhớ Cache (Phần 3)

Tìm hiểu cách làm việc của bộ nhớ Cache (Phần 3) ![]() Tìm hiểu cách làm việc của bộ nhớ Cache (Phần cuối)

Tìm hiểu cách làm việc của bộ nhớ Cache (Phần cuối)

AI

AI  Hướng dẫn AI

Hướng dẫn AI  ChatGPT

ChatGPT  Gemini

Gemini  Thư viện Prompt

Thư viện Prompt  Công nghệ

Công nghệ  Học IT

Học IT  Tiện ích

Tiện ích

AI

AI  Hướng dẫn AI

Hướng dẫn AI  Công nghệ

Công nghệ  Ứng dụng

Ứng dụng  Hệ thống

Hệ thống  Game - Trò chơi

Game - Trò chơi  iPhone

iPhone  Android

Android  Làng Công nghệ

Làng Công nghệ  Học CNTT

Học CNTT  Hàm Excel

Hàm Excel  Download

Download  Khoa học

Khoa học  Cuộc sống

Cuộc sống