- Tìm hiểu cách làm việc của bộ nhớ Cache (Phần 1)

- Tìm hiểu cách làm việc của bộ nhớ Cache (Phần 2)

- Tìm hiểu cách làm việc của bộ nhớ Cache (Phần 3)

Tập Cache liên kết n dòng

Trong cấu hình này, Cache nhớ được chia thành một vài khối (các tập), mỗi khối gồm có “n” dòng.

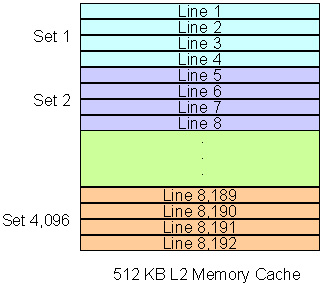

Một tập 4 dòng Cache liên kết thì Cache nhớ sẽ có 2.048 khối, mỗi khối gồm có 4 dòng (8.192 dòng / 4), với tập 2 dòng Cache liên kết thì Cache nhớ sẽ có 4.096 khối, mỗi khối gồm 2 dòng. Chúng ta sẽ tiếp tục ví dụ với Cache nhớ L2 512 KB, Cache nhớ này sẽ chia thành 8.192 dòng, mỗi dòng 64-byte. Phụ thuộc vào CPU mà số khối có thể khác nhau.

Hình 7: Cache nhớ L2 512 KB khi được cấu hình thành một tập 4 dòng liên kết

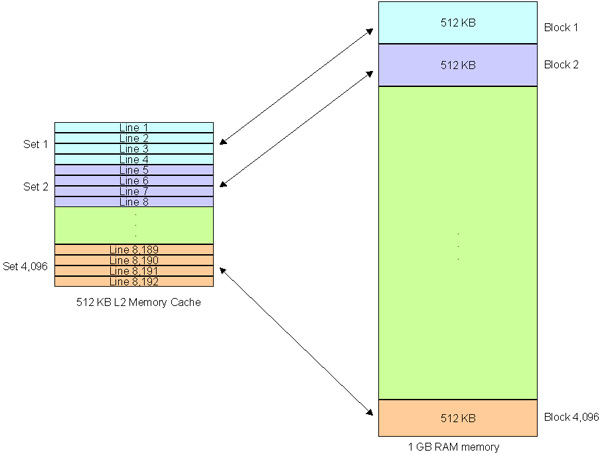

Khi bộ nhớ RAM được chia thành các khối bằng nhau trong Cache nhớ. Vẫn ví dụ tập 4 dòng 512 KB liên kết, RAM chính sẽ được chia thành 2.048 khối nằm trong Cache nhớ. Mỗi khối nhớ lại được liên kết đến một tập các dòng bên trong Cache, giống như trong Cache đã được bản đồ hóa trực tiếp. Với 1GB, bộ nhớ sẽ được chia thành 2.048 khối, mỗi khối 512KB, bạn có thể xem trong hình 8.

Hình 8: Cache nhớ L2 512 KB được cấu hình thành một tập 4 dòng liên kết

Như những gì bạn có thể thấy được, việc bản đồ hóa là hoàn toàn giống với những gì xảy ra với Cache được bản đồ hóa trực tiếp, sự khác biệt ở đây là mỗi một khối nhớ hiện có nhiều dòng trên cùng một Cache. Mỗi một dòng lại giữ nhiều nội dung từ các địa chỉ bên trong các khối đã được bản đồ hóa. Trên tập 4 dòng liên kết, mỗi tập trên Cache nhớ có thể giữ đến 4 dòng từ cùng một khối nhớ.

Với phương pháp này, các vấn đề gặp phải đối với phương pháp bản đồ hóa trực tiếp không còn nữa (cả các vấn đề xung đột do vòng lặp mà chúng ta đã mô tả trên). Ở đây, tập Cache liên kết dễ dàng thực thi hơn so với Cache liên kết toàn bộ, vì logic điều khiển của nó đơn giản hơn. Vì điều đó mà phương pháp này được sử dụng nhiều ngày nay, mặc dù nó cung cấp hiệu suất thấp hơn so với cách liên kết toàn bộ.

Rõ ràng chúng ta vẫn có một số lượng hạn chế các khe bên trong mỗi một tập Cache nhớ đối với mỗi một khối nhớ - 4 trên cấu hình 4 dòng. Sau khi 4 khe này được sử dụng, bộ điều khiển Cache sẽ phải giải phóng một trong số chúng để lưu chỉ lệnh kế tiếp đã được nạp từ cùng khối nhớ.

Khi chúng ta tăng số dòng thì Cache nhớ tập liên kết (ví dụ với cấu hình 4 hoặc 8) sẽ có nhiều khe có sẵn hơn trên mỗi tập, tuy nhiên nếu giữ nguyên số lượng của Cache nhớ thì kích thước của mỗi khối nhớ cũng sẽ tăng. Tiếp tục ví dụ của chúng ta, việc chuyển từ 4 dòng sang 8 dòng sẽ làm cho bộ nhớ 1GB RAM có thể được chia thành 1.024 khối 1MB. Vì vậy cách làm này sẽ tăng số khe có sẵn trên mỗi một tập nhưng mỗi tập lúc này phải chịu trách nhiệm với một khối nhớ lớn hơn.

Có rất nhiều thảo luận trừu tượng liên quan đến việc cân bằng hoàn hảo giữa số các tập và kích thước khối nhớ và tất cả đều chưa có câu trả lời thích đáng - Intel và AMD cũng sử dụng các cấu hình khác nhau, bạn có thể xem trong bảng bên dưới.

Vậy điều gì sẽ xảy ra nếu chúng ta có một Cache nhớ lớn? Vẫn giữ ví dụ ở trên, nếu chúng ta tăng Cache nhớ L2 từ 512 KB thành 1MB (chỉ có một cách thực hiện là thay thế một CPU mới), thì điều xảy ra là chúng ta sẽ có 16.384 dòng 64 byte trong Cache nhớ, điều đó cho chúng ta có đến 4.096 tập và mỗi tập có 4 dòng. Bộ nhớ 1MB RAM của chúng ta sẽ được chia thành 4.096 khối 256MB. Vì vậy về cơ bản những gì xảy ra là kích thước của mỗi khối nhớ giảm hơn và tăng số lần dữ liệu được yêu cầu nằm bên trong Cache nhớ - hay nói cách khác, tăng kích thước Cache sẽ làm giảm được tốc độ miss đối với Cache.

Tuy vậy, việc tăng Cache nhớ không phải là điều bảo đảm cho việc tăng hiệu suất. Tăng kích thước của bộ nhớ Cache chỉ cho phép có nhiều hơn dữ liệu được lưu trữ nhưng một câu hỏi đặt ra là liệu CPU sẽ sử dụng dữ liệu mở rộng đó hay không. Ví dụ, cho một CPU một lõi có Cache L2 4MB. Nếu CPU sử dụng nghiêng về 1MB là chủ yếu còn không quá nặng về phía 3MB kia (nghĩa là hầu hết các chỉ lệnh đã truy cập sẽ chiếm 1MB và trên 3 MB kia CPU đã chứa các chỉ lệnh không được gọi đến nhiều), lúc này CPU sẽ có hiệu suất giống với một CPU chỉ có 2 MB hoặc thậm chí Cache nhớ L2 1MB.

Cấu hình Cache nhớ trên các CPU hiện nay

Dưới đây chúng tôi trình bày cho các bạn một bản tham chiếu gồm có các chi tiết kỹ thuật của Cache nhớ đối với các CPU hiện đang có trên thị trường.

| CPU | Cache chỉ lệnh L1 | Cache dữ liệu L1 | L2 Cache L2 |

| Athlon 64 | 64 KB Tập liên kết 2 dòng Mỗi dòng 64 byte Đường dữ liệu 128 – bit cho L2 Đường dữ liệu 128 – bit cho khối tìm nạp | 64 KB Tập liên kết 2 dòng Mỗi dòng 64 byte Đường dữ liệu 128 – bit cho L2 | 512 KB hoặc 1 MB Tập liên kết 16 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache dữ liệu L1 Đường dữ liệu 128 – bit cho Cache chỉ lệnh L1 |

| Athlon 64 FX | 64KB trên mỗi lõi Tập liên kết 2 dòng Mỗi dòng 64 byte Đường dữ liệu 128 – bit cho L2 Đường dữ liệu 128 – bit cho khối tìm nạp | 64KB trên mỗi lõi Tập liên kết 2 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache L2 | 1MB trên mỗi lõi Tập liên kết 16 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache dữ liệu L1 Đường dữ liệu 128 – bit cho Cache chỉ lệnh L1 |

| Athlon 64 X2 | 64KB trên mỗi lõi Tập liên kết 2 dòng Mỗi dòng 64 byte Đường dữ liệu 128 – bit cho L2 Đường dữ liệu 128 – bit cho khối tìm nạp | 64KB trên mỗi lõi Tập liên kết 2 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache L2 | 512KB hoặc 1MB trên mỗi lõi Tập liên kết 16 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache dữ liệu L1 Đường dữ liệu 128 – bit cho Cache chỉ lệnh L1 |

| Sempron (sockets 754 and AM2) | 64KB Tập liên kết 2 dòng Mỗi dòng 64 byte Đường dữ liệu 128 – bit cho L2 Đường dữ liệu 128 – bit cho khối tìm nạp | 64KB trên mỗi lõi Tập liên kết 2 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache L2 | 128 KB hoặc 256 KB Tập liên kết 16 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache dữ liệu L1 Đường dữ liệu 128 – bit cho Cache chỉ lệnh L1 |

| Opteron | 64KB trên mỗi lõi Tập liên kết 2 dòngĐường dữ liệu 128 – bit cho L2 Đường dữ liệu 128 – bit cho khối tìm nạp | 64KB trên mỗi lõi Tập liên kết 2 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache L2 | 1MB trên mỗi lõi Tập liên kết 16 dòng Mỗi dòng 64byte Đường dữ liệu 128 – bit cho Cache dữ liệu L1 Đường dữ liệu 128 – bit cho Cache chỉ lệnh L1 |

| Pentium 4 | N/A * | 8KB Tập liên kết 4 dòng Mỗi dòng 64byte Đường dữ liệu 256 – bit cho Cache L2 | 256 KB, 512 MB hoặc 1 MBTập liên kết 16 dòng Mỗi dòng 128 byte Đường dữ liệu 64 – bit cho khối tìm nạp Đường dữ liệu 256 – bit cho Cache dữ liệu L1 |

| Pentium D | N/A * | 16KB Tập liên kết 4 dòng Mỗi dòng 64byte Đường dữ liệu 256 – bit cho Cache L2 | 1 MB hoặc 2 MB trên mỗi lõi Tập liên kết 8 dòng Mỗi dòng 128 byte Đường dữ liệu 64 – bit cho khối tìm nạp Đường dữ liệu 256 – bit cho Cache dữ liệu L1 |

| Core 2 Duo | 32 KB Mỗi dòng 64 byte Đường dữ liệu 256 – bit cho khối tìm nạp | 32 KB Mỗi dòng 64 byte Đường dữ liệu 256 – bit cho Cache L2 | 2 MB hoặc 4 MB Tập liên kết 8 dòng Mỗi dòng 64 byte Đường dữ liệu 256 – bit cho Cache dữ liệu L1 |

| Pentium Dual Core | 32 KB Mỗi dòng 64 byte Đường dữ liệu 256 – bit cho khối tìm nạp | 32 KB Mỗi dòng 64 byte Đường dữ liệu 256 – bit cho Cache L2 | 1MB Tập liên kết 8 dòng Mỗi dòng 64 byte Đường dữ liệu 256 – bit cho Cache dữ liệu L1 |

*N/A: Có Cache lần vết 150 KB trên mỗi bộ vi xử lý. Cache này được đặt giữa khối giải mã và khối thực thi. Như vậy khối tìm nạp sẽ lấy dữ liệu trực tiếp từ Cache nhớ L2.

Chúng tôi không giới thiệu các bộ vi xử lý Xeon và Celeron trong bảng trên vì có một số mô hình của Xeon và Celeron khác được dựa trên các kiến trúc khác. Xeon và Celeron được xây dựng trên kiến trúc Netburst (nghĩa là dựa trên kiến trúc Pentium 4) sẽ có các chỉ tiêu kỹ thuật tương tự như Pentium 4 nhưng có kích thước Cache L2 khác đôi chút, còn Celeron và Xeon được xây dựng trên kiến trúc Core (nghĩa là dựa trên Core 2 Duo) sẽ có các chi tiết kỹ thuật giống với Core 2 Duo nhưng có kích thước Cache L2 khác.

AI

AI  Hướng dẫn AI

Hướng dẫn AI  ChatGPT

ChatGPT  Gemini

Gemini  Thư viện Prompt

Thư viện Prompt  Công nghệ

Công nghệ  Học IT

Học IT  Tiện ích

Tiện ích

Làng Công nghệ

Làng Công nghệ  Chuyện công nghệ

Chuyện công nghệ

AI

AI  Hướng dẫn AI

Hướng dẫn AI  Công nghệ

Công nghệ  Ứng dụng

Ứng dụng  Hệ thống

Hệ thống  Game - Trò chơi

Game - Trò chơi  iPhone

iPhone  Android

Android  Học CNTT

Học CNTT  Hàm Excel

Hàm Excel  Download

Download  Khoa học

Khoa học  Cuộc sống

Cuộc sống