Trong nỗ lực cạnh tranh với TSMC đồng thời đưa hoạt động kinh doanh chất bán dẫn của mình lên một tầm cao mới, Samsung đã sẵn sàng ra mắt các công nghệ 3nm và 4nm của mình tại Hội nghị chuyên đề VLSI 2023 (VLSI Symposium 2023) diễn ra vào tháng 6 tới đây. Trọng tâm chính mà gã khổng lồ công nghệ Hàn Quốc nhắm đến trong kế hoạch này là lợi ích của các quy trình SF3 và SF4X mới, cũng như cách thức mà những bộ xử lý phát triển trên các quy trình này sẽ cạnh tranh trên thị trường.

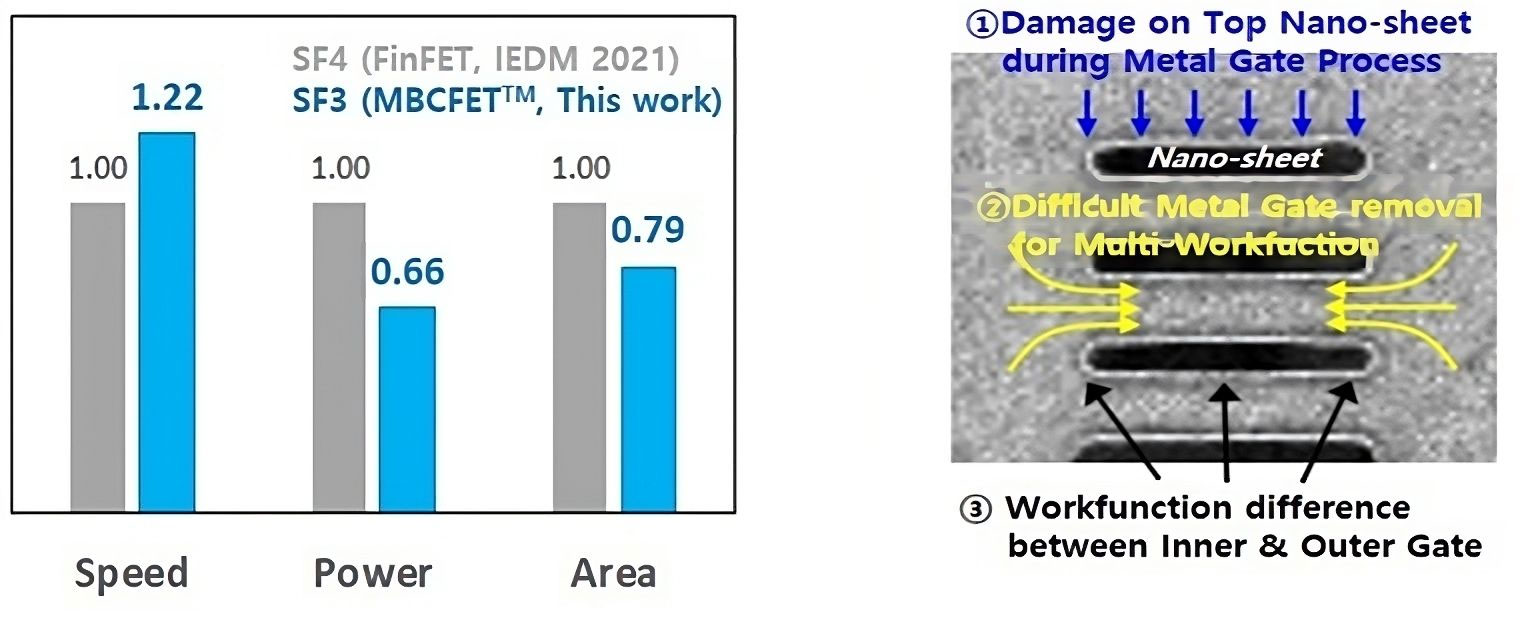

Cụ thể, quy trình SF3 sẽ sử dụng công nghệ GAP 3nm của Samsung và sẽ dựa vào bóng bán dẫn GAA (Gate All Around) mà nhà sản xuất gọi là MBCFET. Cách tiếp cận này được cho là sẽ mang lại nhiều cải tiến hơn nữa so với những quy trình 3nm hiện nó. Nhưng thật kỳ lạ, Samsung đã không so sánh trực tiếp công nghệ này với thế hệ 3nm đầu tiên của mình, cho thấy sự khác biệt có lẽ là không nhiều.

Đối với SF4X, đây là quy trình 4nm thế hệ thứ tư của Samsung, với mức cải thiện hiệu suất 10% và khả năng tiết kiệm năng lượng hơn 23% so với SF4, tức là quy trình 4nm thế hệ thứ hai của hãng. SF4X sẽ cạnh tranh trực tiếp với công nghệ N4P của TSMC, được cho là đang được sử dụng để sản xuất hàng loạt dòng vi xử lý Snapdragon 8 Gen 3 và Dimensity 9300 sắp tới.

Xét về tổng thể, quy trình SF3 được cho là sẽ cho hiệu suất nhanh hơn 22% so với SF4 khi hoạt động ở cùng giới hạn nguồn, và hiệu quả hơn 34% khi chạy ở cùng tần số và số lượng bóng bán dẫn.

Theo lộ trình mà Samsung công bố, quy trình SF3 dự kiến sẽ được sản xuất hàng loạt vào năm 2024, sau đó sẽ có phiên bản nâng cao của SF3P, tức là 3GAP+, sẽ được sản xuất hàng loạt vào năm 2025.

Trong tương lai, sẽ có các quy trình SF2 và SF2P ở nút 2nm và thậm chí quy trình SF1.4 ở nút 1.4nm sẽ được lên kế hoạch vào năm 2027.

AI

AI  Hướng dẫn AI

Hướng dẫn AI  ChatGPT

ChatGPT  Gemini

Gemini  Thư viện Prompt

Thư viện Prompt  Công nghệ

Công nghệ  Học IT

Học IT  Tiện ích

Tiện ích

Làng Công nghệ

Làng Công nghệ  Bảo mật mạng

Bảo mật mạng  Chuyện công nghệ

Chuyện công nghệ  Công nghệ mới

Công nghệ mới  Trí tuệ Thiên tài

Trí tuệ Thiên tài

AI

AI  Hướng dẫn AI

Hướng dẫn AI  Ứng dụng

Ứng dụng  Hệ thống

Hệ thống  Game - Trò chơi

Game - Trò chơi  iPhone

iPhone  Android

Android  Hàm Excel

Hàm Excel  Download

Download  Khoa học

Khoa học  Cuộc sống

Cuộc sống